A Fast Single-pass L1 Cache Simulation Approach for Embedded Processors with Round-robin Replacement Policy. It is faster than random access memory and the data or instructions that the CPU has recently or most frequently used are buffered.

Cache Memory Design Geeksforgeeks

Cache memory is small and fast while the main memory is big and slow.

. It is designed to speed up data transfer and instructions. Power consumption and reusability Which of the following is a property of. Size and replacement policy O c.

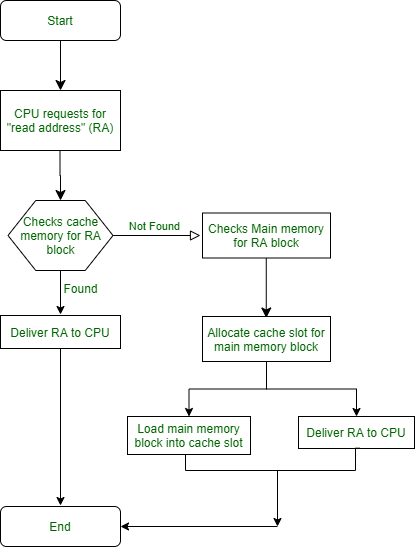

What are some other terms for kernel mode. Embedded Systems Cache Memory Design Issues Performance Evaluation Memory Systems Memory hierarchy characterization of SPEC CPU2006 and SPEC CPU2017 on the Intel Xeon Skylake-SP SPEC CPU is one of the most common benchmark suites used in computer architecture research. The concept of caching is explained below.

Size and access privileges O b. The cache pronounced money is a small fast cache. See answer 1 Best Answer.

Embedded systems designers are free to choose the most suitable configuration of L1 cache in modern processor based SoCs. B Size and replacement policy. Cache memory performance is often the limiting factor in CPU performance and cache memories also serve to cut the memory traffic in multiprocessor systems.

A Speed and volatility B Size and replacement policy C Power consumption and reusability D Size and access privileges. Cells and Chips Memory boards and modules Two-level memory hierarchy The cache. -Logical CacheVirtual Cache stores data using virtual addresses.

-Physical Cache stores data. The simplest such organization is known as a two-level cache with the internal cache designated as level 1 L1 and the external cache designated as level 2 L2. The intent of cache memory is to provide the fastest access to resources without compromising on.

Design issues Cache capacity Cache line size Degree of associatively. Solaris is open source. We are going to see that similar style problems should be self-addressed in addressing storage and cache style.

Two important design issues for cache memory are Select one. Recent papers in Cache Memory Design Issues. All open source operating systems share the same set of goals.

Virtually all modern operating systems provide support for SMP. It is located in or near the CPU chip. There are many different design parameters that are important to a caches overall performance.

Cache Memory Design Issues. There are two design issues surrounding number of caches. Speed and volatility O d.

They are always more secure than commercial closed systems. Registers Memory Disk. The cache fetch algorithm demand versus prefetch the.

Size and replacement policy ____ operating systems are designed primarily to maximize resource utilization. CPU loads MAR and MDR asserts Write and REQUEST. Specific aspects of cache memories that are investigated include.

Main Memory asserts COMPLETE. Want this question answered. 1 Two important design issues for cache memory are a speed and volatility b size.

1 cycle 4 Calculate the total number of bits required for the cache listed above. What are two important design issues for cache memory. A detailed discussion of the cache style is given in this article.

Quiz_1 - Quiz1 Topic Chapter one Two important design issues for cache memory areA power consumption and reusabilityB size and access privilegesC. Source code is freely available. 2 words Cache Access Time.

Cache memory is a small amount of fast memory Placed between two levels of memory hierarchy To bridge the gap in access times Between processor and main memory our focus. They represent the subsequent categories. Cache Memory Design Issues.

CPU loads MAR issues Read and REQUEST 2. Two important design issues for cache memory are ____. A in volatile memory B on one or more disks C in read only memory units D in sequential circuits 6.

What two important design issues for cache memory are. 7-1 Chapter 7- Memory System Design. Be notified when an answer is posted.

Accesses cache directly without going through MMU. The effective and efficient use of the memory hierarchy of the computer system is one of the if not the single most important aspect of computer system design and use. A speed and volatility B size and replacement policy C power consumption and reusability D size and access privileges 5.

Most contemporary designs include both on-chip and external caches. Below are listed parameters for different direct-mapped cache designs. Cache Memory plays a significant role in reducing the processing time of a program by provide swift access to datainstructions.

Main Memory transmits words to MDR 3. Cache Memory Design. These heuristics identify important items that have been requested from memory and copy those items into the cache.

A bootstrap program is stored _____. Cache size Block size Mapping function Replacement. Two important design issues for cache memory are _____.

Two important design issues for cache memory are ____. The key elements are concisely summarized here. 32 KiB Cache Block Size.

Two examples of content heuristics are prefetching data items that are deemed important or soon to be used and replacement policies that decide what items get replaced when a cache set is full or near capacity. 5 CS 135 A brief description of a cache Cache next level of memory hierarchy up from register file ¾All values in register file should be in cache Cache entries usually referred to as blocks ¾Block is minimum amount of information that can be in cache ¾fixed size collection of data retrieved from memory and placed into the cache Processor generates request for.

Solved Two Important Design Issues For Cache Memory Are Chegg Com

10 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Course Hero

1 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Size Course Hero

Solved Two Important Design Issues For Cache Memory Are Chegg Com

Elements Of Cache Design Quick Cse

Concept Of Cache Memory Design Geeksforgeeks

Computer Architecture Organization Cache Memory Design Issues By Sanjay Santokee Medium

Solved Two Important Design Issues For Cache Memory Are Chegg Com

0 comments

Post a Comment